# Selective Harmonic Elimination based THD Minimization of a symmetric 9- Level Inverter using Ant Colony Optimization

Devineni Gireesh Kumar<sup>1,2</sup>, Aman Ganesh<sup>2\*</sup>

<sup>1,2</sup>Department of Electrical and Electronics Engineering, BVRIT, Narsapur, Telangana, India <sup>2\*</sup>School of Electronics and Electrical Engineering, Lovely Professional University, Phagwara, Punjab, India

#### Abstract

A new topology of a symmetric single-phase multilevel inverter with the less number of semiconductor switches and optimized low-frequency control methods to optimize the Total Harmonic Distortion is proposed in this paper. A nine level single phase output is obtained by eight numbers of active semiconductor switches, four diodes and four capacitors from two symmetrical dc sources. The selected harmonic order in the output voltage is eliminated by the PWM (SHE-PWM) based on selective harmonic elimination. To optimize the switching angles, an ant colony optimization is applied. The proposed SHE-PWM and ant optimization are implemented and tested for THD on the SIMULINK platform. The proposed approach offers less THD and is best suited to high-power applications with medium voltage.

Keywords: THD, SHE-PWM, ACO, Multi- Level Inverter.

#### 1. Introduction

Inverter is a system that converts the DC to AC with acceptable voltage and output frequency. Inverters have some inherent issues of lower efficiency, high dv/dt, higher power losses and large THD [1]. A multilevel inverter is designed to solve these issues. With a three-level converter, the word Multilevel has begun, the cascaded multilevel inverter is currently in use [2]. The output of the multi-level inverter has lower harmonics than the normal output voltage of the bipolar inverter. Multilevel inverters are mainly known as a clamped diode, Flying condenser, and cascaded MLI [2-3]. The control scheme of cascaded MLI is simple compared to other MLIs, since a clamping diode and a flying condenser are not needed [5]. For more than three decades, multi-level inverters are under research and development, and successful industrial applications have been discovered [4-5]. Nonetheless, this is still an emerging technology, and many fresh developments have been reported in recent years [6]–[8]. Multilevel inverters have drawn growing interest, with the key reasons being: increasing power levels, improved harmonic performance and reduced emissions of electromagnetic interference (EMI) that can be preserved with several dc stages synthesizing the output voltage waveform [7]. In systems like industrial variable-voltage drives, EVs and photovoltaic networks connected to the grid. The ongoing work offers an alternative to the design of an effective multi-level topology for high and medium-power applications.

Advanced Multi-level inverters now use fewer components and smaller carrier signals as compared with traditional multi-level inverters. A composite topology is presented in this paper having separate level generating part and polarity generating parts [8]. To increase the output of multilevel inverters in hybrid topology, first positive rates are produced with high-frequency switches and then the voltage portion is reversed with low-frequency switches. As a result, the control circuit complexity for higher levels is significantly reduced. Selective harmonic pulse width modulation (SHE-PWM) technique with Ant Colony optimization has been used to simulate a single phase 9-level hybrid inverter. The inverter performance is evaluated with regard to harmonic distortion (THD) [9-10]. The harmonic distortion generated by the proposed inverter is significantly lower, around 5% by the results obtained from simulation.

## 2. Proposed Symmetric Inverter Topology

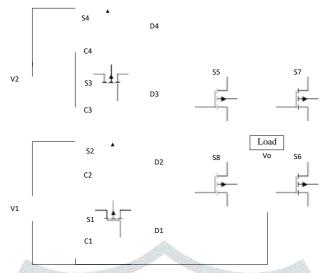

The proposed inverter's schematic design is shown in figure (1), which consists of two modules, namely a module for level generation and a module for voltage reversal / polarity generation. Polarity generation module is an H-bridge that reverses the polarity of output for each half cycle of operation, where as the level generating module will generate higher levels from the dc sources that can extend up to 'n'

levels. Symmetric dc sources are used for the inverter input, where each source is divided into two equal parts by using similar condensers to increase the higher output level from less dc sources. A MOSFET is used for the circuit design and the diodes used in the circuit to prevent the short circuit of the sources.

Figure (1): Proposed Symmetric 9-Level Inverter

Relation between the components used in the circuit design given as follows; No. of capacitors  $(N_c) = 2 N_v$ , Where  $N_v = No.$  of voltage sources No. of Switches

$(N_s) = N_c + 4$

No. of diodes  $(N_d) = N_c$

No. of levels  $(N_{\text{step}}) = 2N_c + 1$

There are nine modes of operation of this inverter to achieve the required 9-level output Vo; the first four modes of operation give the positive levels of voltages, V/2, V, 3V/2, 2V and next four modes of operation give the negative levels of voltages, -V/2, -V, -3V/2, -2V and ninth mode gives the output '0V'is obtained by switching sequence mentioned in table (I).

| Mode | S1 | S2 | S3 | S4 | S5 | <b>S6</b> | S7 | <b>S8</b> | O/P Voltage |

|------|----|----|----|----|----|-----------|----|-----------|-------------|

| I    | 1  | 0  | 0  | 0  | 1  | 1         | 0  | 0         | V/2         |

| II   | 0  | 1  | 0  | 0  | 1  | 1         | 0  | 0         | ${f V}$     |

| III  | 0  | 0  | 1  | 0  | 1  | 1         | 0  | 0         | (3/2)V      |

| IV   | 0  | 0  | 0  | 1  | 1  | 1         | 0  | 0         | 2V          |

| V    | 1  | 0  | 0  | 0  | 0  | 0         | 1  | 1         | -V/2        |

| VI   | 0  | 1  | 0  | 0  | 0  | 0         | 1  | 1         | -V          |

| VII  | 0  | 0  | 1  | 0  | 0  | 0         | 1  | 1         | -(3/2)V     |

| VIII | 0  | 0  | 0  | 1  | 0  | 0         | 1  | 1         | -2V         |

| IX   | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 0         | 0           |

Table 1: Switching Sequence of the all modes of operations

## 3. Selective Harmonic Elimination based control of proposed inverter

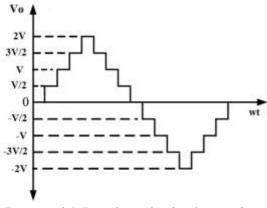

This paper proposed a SHE-PWM to reduce the dominant harmonics of lower order and the switching losses in the proposed hybrid multi level inverter [11]. A synthesized near sinusoidal output expected to obtain from the 9-level output is shown in fig. 2.

# (a) Selective Harmonic Elimination-PWM

Figure 2: Proposed 9-Level synthesized near sinusoidal waveform

For the above 9- level wave form the four switching angles  $\theta_1$ ,  $\theta_2$ ,  $\theta_3$ ,  $\theta_4$  need to be generate. By considering the characteristics of the waveform, these switching angles are the function of Fourier series expression and expressed as (1)

$$V_0 = \sum_{k=1}^{\infty} \frac{4V_{dc}}{k\pi} \left(\cos k\theta + \cos k\theta_2 + + \cos k\theta_n\right) * \sin k\omega t \tag{1}$$

The necessary constraint the to be satisfied the switching angles from  $\theta_1$  to  $\theta_n$  is

$$0 \le \theta < \theta < \theta < \frac{\pi}{2} \qquad (2)$$

Thus with an inverter of nine levels with two DC outputs, the 5th, 7th, and 11th harmonics must be removed, and the transcendental equations to be satisfied are as follows.

$$V_{1} = \cos \theta_{1} + \cos \theta_{2} + \cos \theta_{3} + \cos \theta_{4} = MI$$

$$V_{5} = \cos 5 \theta_{1} + \cos 5 \theta_{2} + \cos 5 \theta_{3} + \cos 5 \theta_{4} = 0$$

$$V_{7} = \cos 7 \theta_{1} + \cos 7 \theta_{2} + \cos 7 \theta_{3} + \cos 7 \theta_{4} = 0$$

$$V_{11} = \cos 1 \theta_{1} + \cos 1 \theta_{2} + \cos 1 \theta_{3} + \cos 1 \theta_{4} = 0$$

For optimum switching angles, modulation index (MI) is;

$$MI = \frac{V_1}{16V_{dc}} \text{ for } 0 \le MI \le 1$$

(3)

The magnitude of the harmonics depends on the angles of switching. To accomplish the above objectives the fitness function (FF) takes the form as follows:

$$FF = 100 * \frac{(V_{1d} - V_1)^4}{V_{1d}^4} + \left(\frac{50}{V_1}\right)^2 * \left|\frac{V^2 V^2}{5 - 7 + \frac{11}{7}}\right| \quad V^2$$

(4)

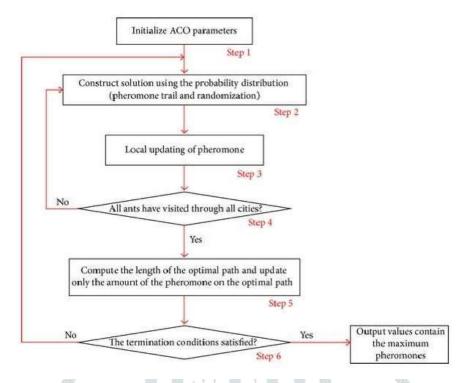

# (b) ANT Optimization of SHE-PWM

Ant optimization (ACO) is the first to investigate an optimal path in an evo utionary-based on ant's behavior to find a path between their colony and food source. Flow chart shown in fig. 3 explains the step by step procedure to be followed to implement the Ant colony optimization algorithm [11-12]

Figure 3: A flow chart for Ant colony optimization

## 4. Results and Discussions:

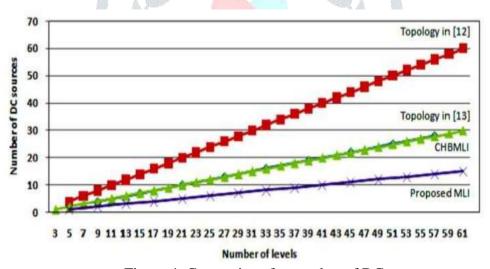

The variance in the number of dc sources needed to model the proposed inverter for different output voltage levels is shown in the fig. 4.

Figure 4: Comparison for number of DC sources

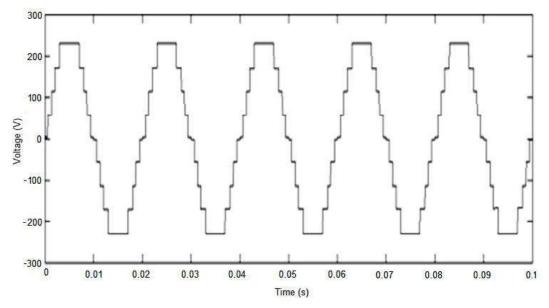

The Switching angles obtained from the Ant colony optimization algorithm. are 9.46°, 19.65°, 36.92° and 59.45° giving a THD of 5.60% The obtained voltage waveform is shown in fig 5.

Figure 5: 9-Level load waveform of proposed inverter

## 4. Conclusions

This paper presented a novel symmetric inverter with reduced switches for a nine level inverter using MATLAB®SIMULINK. To optimize the switching angles of the multi-level inverter, a low frequency switching modulation called SHE-PWM is used to reduce switching losses and THD. In addition, less THD is achieved by adopting the Ant Colony Optimization technique. The output voltage obtained is approximately a sinusoidal wave. The inverter output voltage indicates lower THD. The suggested inverter is compliant with different single-phase applications.

## References

- [1] L. M. Tolbert, F. Z. Peng, D. J. Adams, J. W. Mckeever, and A. Background, "Multilevel Inverters for Large Automotive Electric Drives," vol. 2, (2009), pp. 209-214.

- [2] E. Villanueva, P. Correa, J. Rodriguez, and M. Pacas, "Control of a Single-Phase Cascaded H-Bridge Multilevel Inverter for Grid- Connected Photovoltaic Systems," IEEE Trans. Ind. Electron., vol. 56, no. 11, (2009), pp. 4399–4406.

- [3] J. D. van Wyk and F. C. Lee, "On a Future for Power Electronics," IEEE J. Emerg. Sel. Top. Power Electronics., vol. 1, no. 2, (2013), pp. 59–72.

- J. Holtz, "Pulsewidth modulation A survey," IEEE Trans. Ind. Electron., vol. 39, no. 5, (1992), pp. 410–420.

- [5] Zhong. Du, L. M. Tolbert, B. Ozpineci, and J. N. Chiasson, "Fundamental frequency switching strategies of a seven-level hybrid cascaded H- bridge multilevel inverter," IEEE Trans. Power Electron., vol. 24, no. 1, (2009), pp. 25–33.

- [6] D. Nazarpour, M. Sabahi, R. S. Alishah, and S. H. Hosseini, "New hybrid structure for multilevel inverter with fewer number of components for high-voltage levels," IET Power Electron., vol. 7, no. 1, (2014),pp. 96-104.

- Y. Liu, H. Hong, and A. Q. Huang, "Real-time calculation of switching angles minimizing THD for multilevel inverters with step modulation," IEEE Trans. Ind. Electron., vol. 56, no. 2, (2009), pp. 285-293.

- [8] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel inverter topologies with reduced device count: A review," IEEE Trans. Power Electron., vol. 31, no. 1, (2016), pp. 135–151.

- [9] B. Rajesh and Manjesh "Comparison of Harmonics and THD Suppression with Three and 5 Level Multilevel Inverter-Cascaded H-bridge" IEEE International Conference on Circuit, Power and Computing Technologies [ICCPCT], (2016), pp 1-6.

- [10] C. Gupta, N. Verma, Abhishek and S. Shukla "THD Analysis Of Eleven Level Cascaded H-bridge Multilevel Inverter With Different Types of Load Using In Drives Applications "IEEE Second International Conference on Advances in Computing and Communication Engineering, (2015), pp 355-359.

- [11] M. Babaei and H. Rastegar, "Selective harmonic elimination PWM using ant colony optimization," 2017 Iranian Conference on Electrical Engineering (ICEE), Tehran, (2017), pp. 1054-1059.

- [12] S. D. Patil, S. G. Kadwane and S. P. Gawande, "Ant Colony Optimization applied to selective harmonic elimination in Multilevel inverters," 2016 2nd International Conference on Applied and Theoretical Computing and Communication Technology, Bangalore, (2016), pp. 637-640.